HDI PCB设计中的阻抗匹配

HDI PCB设计中的阻抗匹配

阻抗匹配是配置负载输入阻抗或其信号源输出阻抗的方式。执行它以实现最大功率传输并减少来自负载的信号反射。换句话说,为了适当的阻抗控制,负载阻抗必须等于传输线的特征阻抗。当传输的信号没有反射时,表明负载已经吸收了所有的信号。HDI 中的阻抗匹配完全是为了避免传输故障,尤其是由于电阻和 PCB电介质造成的损耗。

微孔可用于为阻抗匹配系统创建便于生产的 PCB走线。BGA逃逸布线技术和狗骨扇出结构可用于在 HDI 中实现阻抗匹配。

PCB走线何时需要阻抗匹配?

阻抗匹配由信号的陡度和上升/下降时间决定,而不是由频率决定。如果信号的上升/下降时间(以 10% 至 90% 为基准)短于迹线延迟的6 倍,则称为高速信号。在这里,应该进行精确的阻抗匹配。

HDI阻抗匹配的挑战

在 HDI 中实现阻抗匹配时,设计人员会遇到以下挑战:

在高密度互连HDI PCB设计中,组件具有较小的焊盘到焊盘间距,例如 BGA。间距小于或等于 0.65 毫米的 BGA 使布线和控制其宽度具有挑战性。在这种情况下,可以使用焊盘内过孔和 BGA 逃逸布线技术。

带有盲孔的焊盘中的过孔是一个优势,因为它们避免了过孔残端,从而提高了信号完整性。

在需要阻抗控制布线的 HDI 板中,精心设计的走线和堆叠对于确保阻抗与信号标准一致至关重要。

为 HDI 阻抗调整设计走线宽度

走线的阻抗由其距参考平面的宽度和高度决定。在使用细间距 BGA 的 HDI 板中,仔细选择走线宽度和高度以避开焊盘和焊盘中通孔之间的走线。

使用 HDI PCB设计中的 BGA 逃逸布线进行阻抗控制

在处理高密度互连时使用了几个 BGA 组件。为了使走线进出高引脚数球栅阵列的底部,需要一种逃逸布线方案。在某些情况下,需要受控阻抗(例如 FPGA 和其他高速组件),BGA 逃逸布线可能具有挑战性。

设计电路板时要使用的逃逸布线策略很大程度上取决于 BGA 间距,它定义了允许放置在焊球之间的走线宽度。走线的细度还取决于制造商的限制、层堆叠和必要的阻抗。选择逃逸路由方案时,请记住以下准则。

用于中等层数的细间距 BGA 的逃逸布线技术从颈缩方法开始,因为迹线被布线进出 BGA。

外部走线可以直接布线到电路板上的第一排焊盘上。

球栅阵列上第二行焊盘的迹线宽度显着减小,以便它可以安装在第一行焊盘之间。

要到达其余行的内垫,请穿过内层。通常,每个信号层路由到两行,同时限制阻抗和HDI 串扰。

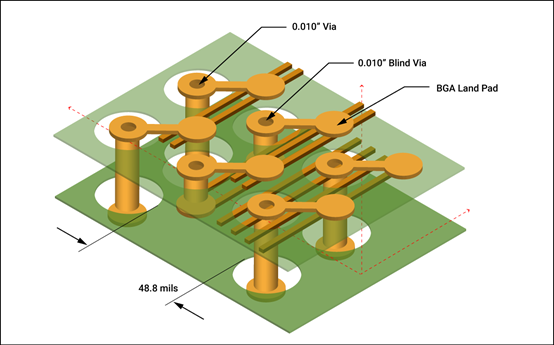

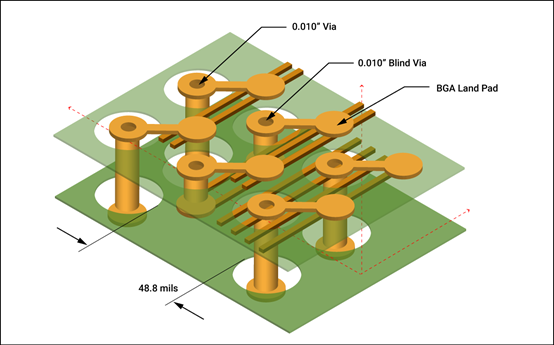

Dogbone fanout 是最流行的 BGA 逃逸布线和扇出方法(如下图所示)。这种扇出技术有助于在更靠近焊盘的焊盘中放置通孔。由于元件不是通过通孔直接焊接到焊盘上,因此不需要进行填充镀覆。1 mm BGA 和 0.8 mm BGA 可能适用于狗骨扇出。

当 BGA 间距小于 0.5 mm 时,最好采用 microvia-in-pad 逃逸布线技术。微通孔直接放置在焊盘中,而不是将小迹线布线到焊盘的侧面。为了防止焊料芯吸到电路板的背面,微孔填充有导电环氧树脂并镀有铜。

用于 BGA 逃逸布线的微孔

如果焊盘尺寸(包括圆环)对于细间距 BGA 来说足够小,则使用微孔进行内层 BGA 逃逸布线。以下特征将微孔与传统孔区分开来:

过孔长度:过孔最多只能穿过一层或两层。如果标准厚度 PCB具有非常高的层数,则通孔可以跨越更多层,但这需要额外的制造程序。尽可能使用跨越单层的堆叠盲孔和埋孔。

微孔纵横比:微孔纵横比(深度除以直径)应为0.75:1。让我们通过考虑 32 层厚板的示例来理解相同的内容。由于层厚(对于 2 层磁芯)为 2 密耳,因此直径不应小于 2.7 密耳。

微通孔只能安全地机械钻孔到 8 密耳,但是由于频繁的钻孔断裂,8 密耳的机械 PCB钻孔费用可以接近激光钻孔的价格。机械通孔的吞吐量低于激光钻孔的通孔,因为必须小心地进行机械钻孔以避免钻头断裂。因此,一旦您开始使用激光钻孔,您就会看到每块板的总成本下降。

要在 0.8 毫米间距 BGA 上使用狗骨扇出,走线宽度必须为 10 密耳或更小,微孔必须更小(约 6 密耳)。对于更细间距的球栅阵列(0.5 毫米),使用填充和电镀的焊盘内微孔通过 7 mil 或 8 mil 走线布线到内层中。这将在相邻焊盘之间提供足够的间距。

无论设计风格如何,微孔都可以堆叠或交错排列,以达到所需的布线密度。通过IPC 6012要求,以确保微孔和周围环形圈的尺寸具有最佳可靠性。焊盘内微孔在 BGA 逃逸布线中的相关性可以通过以下事实来理解:BGA 间距在某些情况下可以低至 0.3 毫米。

如何放置盲孔以进行逃逸布线

内层布线空间的盲孔方法。

盲孔是一种宝贵的 HDI 设计方法,可以释放额外的内层布线空间。当在通孔之间使用时,这些类型的过孔使内层的布线空间加倍。它允许额外的走线连接内部 BGA 行上的引脚。见上图;在这里,在这个 1.0 毫米 BGA 表面上的通孔之间只有两条走线可以逃逸。但是,现在盲孔下方可以有 6 条走线,这将布线空间增加了 30%。

使用这种方法,需要四分之一的信号层来连接高 I/O BGA。盲孔以十字、L 形或对角线图案放置,以形成林荫大道。电源和接地引脚分配决定了使用哪种配置。

以交叉、L 形或对角线形状放置盲孔会在内层上创建林荫大道,以允许更高密度的布线和逃逸。

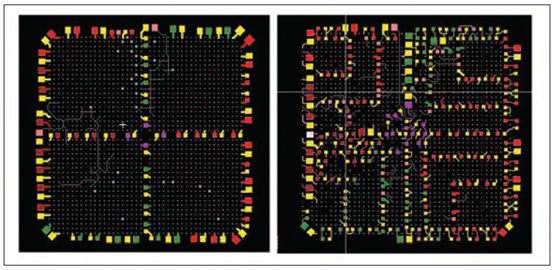

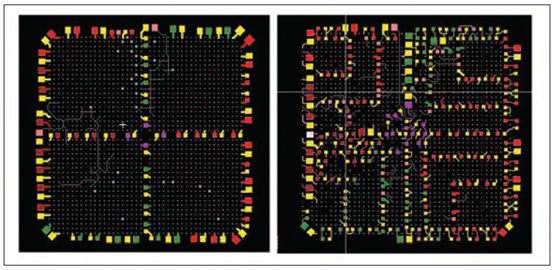

插图显示了放置盲孔以在 BGA 内创建林荫大道以改善突破。左:BGA 的传统 4 象限扇出;右图:添加了十字形盲孔,允许在内层上创建的林荫大道中增加 48 个逃逸通道,从而减少了突破器件所需的 4 个。

Happy Holden 解释说:“每层可以连接更多的走线,还可以通过使用林荫大道创建额外的布线空间来减少信号层的总数。盲孔用于创建四个十字形林荫大道(如图所示)。新设计的林荫大道每层提供 48 个更多的逃逸通道(8 x 6 走线),并提高了内部走线的信号完整性。它允许移除两个布线层和两个参考平面。”

此外,他说:“在电路板的次级侧,可以观察到使用盲孔创建林荫大道的另一个优势。通孔横跨整个电路板,但林荫大道现在在 BGA 内开放(如图所示)。左图显示了由 BGA 下的 104 个过孔连接的 58 个分立器件。在右侧,林荫大道可以通过共享 366 个过孔连接 183 个分立元件。”

这些图显示了两个 BGA 的背面。一种是带有通孔的传统象限扇出,允许 58 个分立器件。另一个利用林荫大道的盲道,其中可以连接 183 个分立元件。

扇出部分长度和走线宽度

在使用高速 IC 时,阻抗几乎总是一个因素。在检查扇出部分的长度时,扇出布线和阻抗控制之间的关系开始发挥作用。由于过孔的走线长度(如果存在)和寄生电容/电感,BGA 扇出部分将具有其阻抗。

首先,检查信号带宽以确定信号是否会在走线阻抗上拾取。如果走线长度明显小于对应于带宽高端的波长,则可以忽略 BGA 扇出的走线部分。最好的方法是计算负载阻抗,它是扇出走线长度的函数,以及由扇出走线创建的网络输入阻抗(颈缩后)。

对信号波长所需的长度使用 10% 的限制作为一个很好的近似值。对拐点频率为 20GHz 的数字信号谨慎的 10% 限制将导致临界长度为 0.73mm(FR4 基板中的带状线)。这意味着更大的 IC,比如 FPGA,需要为单端和差分对提供阻抗匹配的扇出。

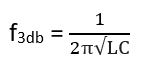

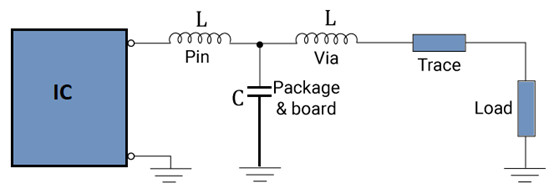

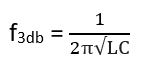

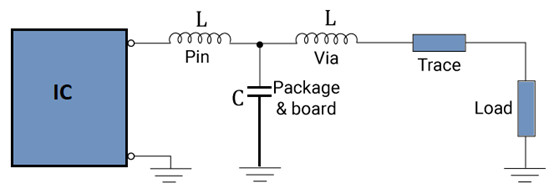

过孔电感、电路板和焊盘之间的寄生电容以及 IC 中的引脚电感至关重要。低通T滤波器电路由这些部分组合而成。3dB 截止频率只是可以从 LC 谐振电路评估的典型数字,前提是通孔电感设置为等于引脚电感。该 T 滤波器电路用作阻抗匹配电路,修改驱动器 IC 的输出阻抗。

以通孔电感、电路板与焊盘之间的寄生电容以及引脚电感为主要部件的低通T滤波器电路。

如果不确定将扇出迹线连接到内部迹线的过孔部分阻抗,则扇出部分的阻抗匹配是困难的。然而,只要过孔部分很短并且直接跨越几层,这个事实就可以被忽略。包括通孔和内部走线在内的总输入阻抗由跨越少量层的内部走线阻抗决定。这就是为什么通常不考虑通孔阻抗的原因。

主要缺点是高速 BGA 组件(例如 FPGA)可能需要回钻以去除 BGA 扇出下方的残留通孔存根。使用 HDI 时,使用直径非常小的盲孔、埋孔和激光钻孔微孔(根据 IPC 小于 6 密耳),这消除了背钻孔并将通孔电感限制在跨越层的厚度。

由于层厚和到走线参考平面的距离会随着层数的增加而减少,因此必须减小走线宽度以补偿并将阻抗保持在适当的值。如果您使用差分对,请考虑走线耦合。为了实现阻抗控制,带有集成场解算器的PCB设计软件可以帮助为 HDI 层堆叠设计正确的走线宽度。

为什么HDI PCB设计中走线宽度不能大于焊盘尺寸?

走线的宽度与其阻抗成正比,并且在您进入 HDI 状态时起着至关重要的作用。过孔将变得非常小,以至于一旦走线宽度足够小,就必须将它们制造为微孔。

如果阻抗控制的走线宽度过宽,要么减小PCB层压板的厚度以缩小它,要么增加焊盘尺寸。从可靠性的角度来看,只要焊盘尺寸超过 IPC 标准中规定的数字就可以了。

为 PCB堆叠创建阻抗曲线,并将该宽度用作设计指南。在计算阻抗控制所需的宽度后,只需将此值指定为设计规则即可。最好针对建议的走线宽度执行串扰模拟,以查看是否会导致过度串扰。

HDI 中的阻抗匹配与保持信号质量有关,因为组件和走线都间隔很近。因此,控制阻抗成为一项令人难以置信的任务。有效使用微孔是阻抗匹配 HDI 系统的关键。更细间距 BGA 的逃逸布线技术和狗骨扇出方法可用于实现 HDI 中的阻抗匹配。

丰乐壹博专业PCB设计、PCB Layout、PCBA一站式生产。

阻抗匹配是配置负载输入阻抗或其信号源输出阻抗的方式。执行它以实现最大功率传输并减少来自负载的信号反射。换句话说,为了适当的阻抗控制,负载阻抗必须等于传输线的特征阻抗。当传输的信号没有反射时,表明负载已经吸收了所有的信号。HDI 中的阻抗匹配完全是为了避免传输故障,尤其是由于电阻和 PCB电介质造成的损耗。

微孔可用于为阻抗匹配系统创建便于生产的 PCB走线。BGA逃逸布线技术和狗骨扇出结构可用于在 HDI 中实现阻抗匹配。

PCB走线何时需要阻抗匹配?

阻抗匹配由信号的陡度和上升/下降时间决定,而不是由频率决定。如果信号的上升/下降时间(以 10% 至 90% 为基准)短于迹线延迟的6 倍,则称为高速信号。在这里,应该进行精确的阻抗匹配。

HDI阻抗匹配的挑战

在 HDI 中实现阻抗匹配时,设计人员会遇到以下挑战:

在高密度互连HDI PCB设计中,组件具有较小的焊盘到焊盘间距,例如 BGA。间距小于或等于 0.65 毫米的 BGA 使布线和控制其宽度具有挑战性。在这种情况下,可以使用焊盘内过孔和 BGA 逃逸布线技术。

带有盲孔的焊盘中的过孔是一个优势,因为它们避免了过孔残端,从而提高了信号完整性。

在需要阻抗控制布线的 HDI 板中,精心设计的走线和堆叠对于确保阻抗与信号标准一致至关重要。

为 HDI 阻抗调整设计走线宽度

走线的阻抗由其距参考平面的宽度和高度决定。在使用细间距 BGA 的 HDI 板中,仔细选择走线宽度和高度以避开焊盘和焊盘中通孔之间的走线。

使用 HDI PCB设计中的 BGA 逃逸布线进行阻抗控制

在处理高密度互连时使用了几个 BGA 组件。为了使走线进出高引脚数球栅阵列的底部,需要一种逃逸布线方案。在某些情况下,需要受控阻抗(例如 FPGA 和其他高速组件),BGA 逃逸布线可能具有挑战性。

设计电路板时要使用的逃逸布线策略很大程度上取决于 BGA 间距,它定义了允许放置在焊球之间的走线宽度。走线的细度还取决于制造商的限制、层堆叠和必要的阻抗。选择逃逸路由方案时,请记住以下准则。

用于中等层数的细间距 BGA 的逃逸布线技术从颈缩方法开始,因为迹线被布线进出 BGA。

外部走线可以直接布线到电路板上的第一排焊盘上。

球栅阵列上第二行焊盘的迹线宽度显着减小,以便它可以安装在第一行焊盘之间。

要到达其余行的内垫,请穿过内层。通常,每个信号层路由到两行,同时限制阻抗和HDI 串扰。

Dogbone fanout 是最流行的 BGA 逃逸布线和扇出方法(如下图所示)。这种扇出技术有助于在更靠近焊盘的焊盘中放置通孔。由于元件不是通过通孔直接焊接到焊盘上,因此不需要进行填充镀覆。1 mm BGA 和 0.8 mm BGA 可能适用于狗骨扇出。

当 BGA 间距小于 0.5 mm 时,最好采用 microvia-in-pad 逃逸布线技术。微通孔直接放置在焊盘中,而不是将小迹线布线到焊盘的侧面。为了防止焊料芯吸到电路板的背面,微孔填充有导电环氧树脂并镀有铜。

用于 BGA 逃逸布线的微孔

如果焊盘尺寸(包括圆环)对于细间距 BGA 来说足够小,则使用微孔进行内层 BGA 逃逸布线。以下特征将微孔与传统孔区分开来:

过孔长度:过孔最多只能穿过一层或两层。如果标准厚度 PCB具有非常高的层数,则通孔可以跨越更多层,但这需要额外的制造程序。尽可能使用跨越单层的堆叠盲孔和埋孔。

微孔纵横比:微孔纵横比(深度除以直径)应为0.75:1。让我们通过考虑 32 层厚板的示例来理解相同的内容。由于层厚(对于 2 层磁芯)为 2 密耳,因此直径不应小于 2.7 密耳。

微通孔只能安全地机械钻孔到 8 密耳,但是由于频繁的钻孔断裂,8 密耳的机械 PCB钻孔费用可以接近激光钻孔的价格。机械通孔的吞吐量低于激光钻孔的通孔,因为必须小心地进行机械钻孔以避免钻头断裂。因此,一旦您开始使用激光钻孔,您就会看到每块板的总成本下降。

要在 0.8 毫米间距 BGA 上使用狗骨扇出,走线宽度必须为 10 密耳或更小,微孔必须更小(约 6 密耳)。对于更细间距的球栅阵列(0.5 毫米),使用填充和电镀的焊盘内微孔通过 7 mil 或 8 mil 走线布线到内层中。这将在相邻焊盘之间提供足够的间距。

无论设计风格如何,微孔都可以堆叠或交错排列,以达到所需的布线密度。通过IPC 6012要求,以确保微孔和周围环形圈的尺寸具有最佳可靠性。焊盘内微孔在 BGA 逃逸布线中的相关性可以通过以下事实来理解:BGA 间距在某些情况下可以低至 0.3 毫米。

如何放置盲孔以进行逃逸布线

内层布线空间的盲孔方法。

盲孔是一种宝贵的 HDI 设计方法,可以释放额外的内层布线空间。当在通孔之间使用时,这些类型的过孔使内层的布线空间加倍。它允许额外的走线连接内部 BGA 行上的引脚。见上图;在这里,在这个 1.0 毫米 BGA 表面上的通孔之间只有两条走线可以逃逸。但是,现在盲孔下方可以有 6 条走线,这将布线空间增加了 30%。

使用这种方法,需要四分之一的信号层来连接高 I/O BGA。盲孔以十字、L 形或对角线图案放置,以形成林荫大道。电源和接地引脚分配决定了使用哪种配置。

以交叉、L 形或对角线形状放置盲孔会在内层上创建林荫大道,以允许更高密度的布线和逃逸。

插图显示了放置盲孔以在 BGA 内创建林荫大道以改善突破。左:BGA 的传统 4 象限扇出;右图:添加了十字形盲孔,允许在内层上创建的林荫大道中增加 48 个逃逸通道,从而减少了突破器件所需的 4 个。

Happy Holden 解释说:“每层可以连接更多的走线,还可以通过使用林荫大道创建额外的布线空间来减少信号层的总数。盲孔用于创建四个十字形林荫大道(如图所示)。新设计的林荫大道每层提供 48 个更多的逃逸通道(8 x 6 走线),并提高了内部走线的信号完整性。它允许移除两个布线层和两个参考平面。”

此外,他说:“在电路板的次级侧,可以观察到使用盲孔创建林荫大道的另一个优势。通孔横跨整个电路板,但林荫大道现在在 BGA 内开放(如图所示)。左图显示了由 BGA 下的 104 个过孔连接的 58 个分立器件。在右侧,林荫大道可以通过共享 366 个过孔连接 183 个分立元件。”

这些图显示了两个 BGA 的背面。一种是带有通孔的传统象限扇出,允许 58 个分立器件。另一个利用林荫大道的盲道,其中可以连接 183 个分立元件。

扇出部分长度和走线宽度

在使用高速 IC 时,阻抗几乎总是一个因素。在检查扇出部分的长度时,扇出布线和阻抗控制之间的关系开始发挥作用。由于过孔的走线长度(如果存在)和寄生电容/电感,BGA 扇出部分将具有其阻抗。

首先,检查信号带宽以确定信号是否会在走线阻抗上拾取。如果走线长度明显小于对应于带宽高端的波长,则可以忽略 BGA 扇出的走线部分。最好的方法是计算负载阻抗,它是扇出走线长度的函数,以及由扇出走线创建的网络输入阻抗(颈缩后)。

对信号波长所需的长度使用 10% 的限制作为一个很好的近似值。对拐点频率为 20GHz 的数字信号谨慎的 10% 限制将导致临界长度为 0.73mm(FR4 基板中的带状线)。这意味着更大的 IC,比如 FPGA,需要为单端和差分对提供阻抗匹配的扇出。

过孔电感、电路板和焊盘之间的寄生电容以及 IC 中的引脚电感至关重要。低通T滤波器电路由这些部分组合而成。3dB 截止频率只是可以从 LC 谐振电路评估的典型数字,前提是通孔电感设置为等于引脚电感。该 T 滤波器电路用作阻抗匹配电路,修改驱动器 IC 的输出阻抗。

以通孔电感、电路板与焊盘之间的寄生电容以及引脚电感为主要部件的低通T滤波器电路。

如果不确定将扇出迹线连接到内部迹线的过孔部分阻抗,则扇出部分的阻抗匹配是困难的。然而,只要过孔部分很短并且直接跨越几层,这个事实就可以被忽略。包括通孔和内部走线在内的总输入阻抗由跨越少量层的内部走线阻抗决定。这就是为什么通常不考虑通孔阻抗的原因。

主要缺点是高速 BGA 组件(例如 FPGA)可能需要回钻以去除 BGA 扇出下方的残留通孔存根。使用 HDI 时,使用直径非常小的盲孔、埋孔和激光钻孔微孔(根据 IPC 小于 6 密耳),这消除了背钻孔并将通孔电感限制在跨越层的厚度。

由于层厚和到走线参考平面的距离会随着层数的增加而减少,因此必须减小走线宽度以补偿并将阻抗保持在适当的值。如果您使用差分对,请考虑走线耦合。为了实现阻抗控制,带有集成场解算器的PCB设计软件可以帮助为 HDI 层堆叠设计正确的走线宽度。

为什么HDI PCB设计中走线宽度不能大于焊盘尺寸?

走线的宽度与其阻抗成正比,并且在您进入 HDI 状态时起着至关重要的作用。过孔将变得非常小,以至于一旦走线宽度足够小,就必须将它们制造为微孔。

如果阻抗控制的走线宽度过宽,要么减小PCB层压板的厚度以缩小它,要么增加焊盘尺寸。从可靠性的角度来看,只要焊盘尺寸超过 IPC 标准中规定的数字就可以了。

为 PCB堆叠创建阻抗曲线,并将该宽度用作设计指南。在计算阻抗控制所需的宽度后,只需将此值指定为设计规则即可。最好针对建议的走线宽度执行串扰模拟,以查看是否会导致过度串扰。

HDI 中的阻抗匹配与保持信号质量有关,因为组件和走线都间隔很近。因此,控制阻抗成为一项令人难以置信的任务。有效使用微孔是阻抗匹配 HDI 系统的关键。更细间距 BGA 的逃逸布线技术和狗骨扇出方法可用于实现 HDI 中的阻抗匹配。

丰乐壹博专业PCB设计、PCB Layout、PCBA一站式生产。

上一新闻:在高速PCB设计中不要跨越地平面间隙

下一新闻:PCB设计放大器接线技巧