射频PCB设计和要考虑的因素

射频PCB设计和要考虑的因素

RF PCB设计可能与传统电路板完全不同。它通过阻抗匹配、类型走线(最好是共面的)、消除过孔(以避免反射)、接地层和过孔以及电源去耦等参数来区分。这些板还具有重要的方面,例如叠层和材料选择。

由于 EMI 干扰和高频信号通道等因素,这些因素使射频设计更加复杂。丰乐壹博PCB设计服务团队是RF PCB设计专家。我们将在本文中详细讨论所有这些问题。让我们从阻抗匹配开始。

阻抗匹配

当阻抗在整个迹线上保持恒定时,受控阻抗无线电电路允许从源到负载的最大功率传输而不会失真。这称为迹线的特性阻抗 (Z )。走线的几何形状决定了特性阻抗。这包括走线宽度、PCB材料的介电常数和走线厚度。此外,从参考平面的高度。PCB设计人员可以通过设计匹配电路来匹配这些阻抗。

射频板材料

某些材料用于制造满足高频操作要求的射频PCB。这些材料必须具有低信号损耗并在高频操作中保持稳定。它们还需要能够吸收大量热量。介电常数 (DK)、损耗角正切(tan-d)和热膨胀系数(CTE) 需要在宽频率范围内保持一致。这些板具有3和 HTML3.5 作为介电常数的典型值。对于10-30GHz频率范围,损耗角正切值范围为 0.0022 - 0.0095。

这些只是一些要求。此外,还要考虑制造的成本和难易程度。

通常使用由聚四氟乙烯(PTFE)、陶瓷和碳氢化合物制成的材料,或与某种玻璃混合。Rogers材料是射频电路板设计的热门选择。罗杰斯的材料种类繁多。下面是几个例子:

逆转录/杜罗

RO3000

RO4000

罗杰斯TMM

射频PCB叠层

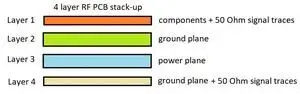

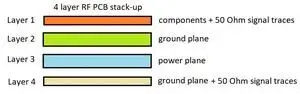

射频板堆叠需要仔细注意组件和走线之间的隔离、电源去耦、层数、排列和放置等细节。下图显示了标准的4层射频叠层。

顶层是放置射频元件和走线的地方。顶层紧随其后的是接地层和电源层。 底层包含所有非射频部分和跟踪信息。 这种安排最大限度地减少了射频和非射频组件之间的干扰。接地层是接地返回电流的最短路径。这种叠层非常适合小型射频板。

射频走线设计

高频信号传播射频迹线,因此容易受到干扰和传输损耗。走线是射频板中的传输线。共面波导、微带线和带状线是最常用的传输线。设计人员关心这些线路的特性阻抗。以下是一些确保正确操作和最小损耗的射频走线设计注意事项。

保持走线尽可能短是至关重要的。这减少了衰减。

切勿在布局中平行放置RF和标准走线。如果两者以这种方式放置,则会产生干扰。

需要接地层来提供信号返回路径。

不建议在迹线上放置测试点。它会破坏走线的阻抗匹配值。

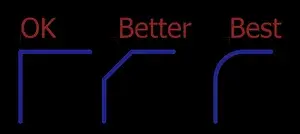

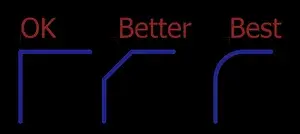

对于跟踪性能,逐渐弯曲比保持急转弯更好。

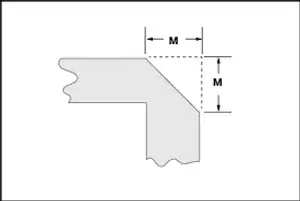

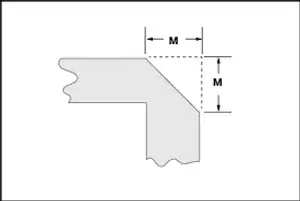

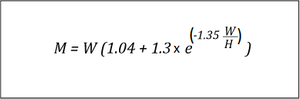

当无法进行右弯时,PCB设计人员可以使用计量过程来减少其影响。下图说明了如何测量迹线。

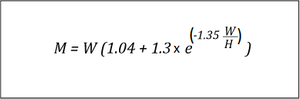

以下公式给出 M:

设计地平面

任何射频迹线或组件都需要返回路径,或者允许电流通过它传播。这是由地平面完成的。接地层需要额外的设计考虑。让我们来看看它们。

每个射频层都应该有一个专用的接地层。为了使电流路径尽可能短,PCB设计人员应将接地层直接放置在每一层的下方。

地平面必须是连续的。不允许休息。这些中断可能会为电流返回的更短路线开辟道路。

必须为放置在射频传输电缆中的每个分流组件安装两个接地过孔。

通过设计

避免射频走线中的过孔应该是重中之重。但是,如果PCB设计人员无法避免这些,则必须遵循特定的过孔尺寸和长度。寄生电容是由电路板中的过孔引起的。在射频板的情况下,该电容会影响高频操作。为了减少这些频率上的干扰,必须在设计过孔时牢记以下准则:

通过引入更多的平行过孔来降低寄生电容

必须将专用过孔连接到组件的每个引脚或焊盘。

尽可能使用地平面缝合。这为电流创建了更短的接地回路。

通孔减少了射频走线从一层到下一层的布线。

该设计允许您在内层和顶层接地层之间使用尽可能多的过孔。 这些过孔必须至少是信号波长的 1/20。

电源去耦

射频板需要降噪才能有效。这些电路板容易受到高频噪声的影响。因此,去除噪声是一项复杂的任务。其中一种方法是电源去耦。

选择去耦电容

该滤波器可消除电源引入电路的任何噪声。这些电容器称为去耦电容器。这些电容器连接到电源。

阻抗匹配应该是每个射频电路板不可或缺的一部分。连接去耦电容后,电路的阻抗应保持恒定。为避免阻抗变化,请遵循以下设计注意事项:

对于去耦,始终连接具有最小阻抗的电容器

要获得最小阻抗,请在自谐振频率(SRF)下运行电容器。电容器的SRF值将与其电容成反比。

寻找SRF接近噪声频率的电容器。

放置去耦电容

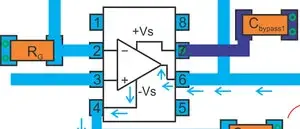

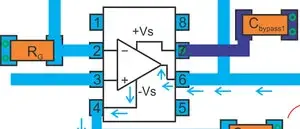

正确放置去耦电容至关重要。下面的电路显示了与IC并联放置的两个去耦电容器。

较高的电容器用于过滤低频噪声和存储能量。较低的电容器滤除高频噪声。这些是其他放置指南:

元件和去耦电容应放置在同一表面上。

将电容器与信号流路径平行放置。

每个电容器都应该有自己的接地通孔。

根据电容升序排列电容器。电容最小的电容离电源最近。

制造商和设计人员都需要更加关注射频板的设计和制造过程。DFM团队应遵循设计清单。这些板容易受到干扰和高频噪声的影响,因此即使是最轻微的错误也会对操作产生重大影响。这些方面和其他方法将帮助我们改进我们的设计。

丰乐壹博专业PCB设计、PCB Layout、PCBA一站式生产.

RF PCB设计可能与传统电路板完全不同。它通过阻抗匹配、类型走线(最好是共面的)、消除过孔(以避免反射)、接地层和过孔以及电源去耦等参数来区分。这些板还具有重要的方面,例如叠层和材料选择。

由于 EMI 干扰和高频信号通道等因素,这些因素使射频设计更加复杂。丰乐壹博PCB设计服务团队是RF PCB设计专家。我们将在本文中详细讨论所有这些问题。让我们从阻抗匹配开始。

阻抗匹配

当阻抗在整个迹线上保持恒定时,受控阻抗无线电电路允许从源到负载的最大功率传输而不会失真。这称为迹线的特性阻抗 (Z )。走线的几何形状决定了特性阻抗。这包括走线宽度、PCB材料的介电常数和走线厚度。此外,从参考平面的高度。PCB设计人员可以通过设计匹配电路来匹配这些阻抗。

射频板材料

某些材料用于制造满足高频操作要求的射频PCB。这些材料必须具有低信号损耗并在高频操作中保持稳定。它们还需要能够吸收大量热量。介电常数 (DK)、损耗角正切(tan-d)和热膨胀系数(CTE) 需要在宽频率范围内保持一致。这些板具有3和 HTML3.5 作为介电常数的典型值。对于10-30GHz频率范围,损耗角正切值范围为 0.0022 - 0.0095。

这些只是一些要求。此外,还要考虑制造的成本和难易程度。

通常使用由聚四氟乙烯(PTFE)、陶瓷和碳氢化合物制成的材料,或与某种玻璃混合。Rogers材料是射频电路板设计的热门选择。罗杰斯的材料种类繁多。下面是几个例子:

逆转录/杜罗

RO3000

RO4000

罗杰斯TMM

射频PCB叠层

射频板堆叠需要仔细注意组件和走线之间的隔离、电源去耦、层数、排列和放置等细节。下图显示了标准的4层射频叠层。

顶层是放置射频元件和走线的地方。顶层紧随其后的是接地层和电源层。 底层包含所有非射频部分和跟踪信息。 这种安排最大限度地减少了射频和非射频组件之间的干扰。接地层是接地返回电流的最短路径。这种叠层非常适合小型射频板。

射频走线设计

高频信号传播射频迹线,因此容易受到干扰和传输损耗。走线是射频板中的传输线。共面波导、微带线和带状线是最常用的传输线。设计人员关心这些线路的特性阻抗。以下是一些确保正确操作和最小损耗的射频走线设计注意事项。

保持走线尽可能短是至关重要的。这减少了衰减。

切勿在布局中平行放置RF和标准走线。如果两者以这种方式放置,则会产生干扰。

需要接地层来提供信号返回路径。

不建议在迹线上放置测试点。它会破坏走线的阻抗匹配值。

对于跟踪性能,逐渐弯曲比保持急转弯更好。

当无法进行右弯时,PCB设计人员可以使用计量过程来减少其影响。下图说明了如何测量迹线。

以下公式给出 M:

设计地平面

任何射频迹线或组件都需要返回路径,或者允许电流通过它传播。这是由地平面完成的。接地层需要额外的设计考虑。让我们来看看它们。

每个射频层都应该有一个专用的接地层。为了使电流路径尽可能短,PCB设计人员应将接地层直接放置在每一层的下方。

地平面必须是连续的。不允许休息。这些中断可能会为电流返回的更短路线开辟道路。

必须为放置在射频传输电缆中的每个分流组件安装两个接地过孔。

通过设计

避免射频走线中的过孔应该是重中之重。但是,如果PCB设计人员无法避免这些,则必须遵循特定的过孔尺寸和长度。寄生电容是由电路板中的过孔引起的。在射频板的情况下,该电容会影响高频操作。为了减少这些频率上的干扰,必须在设计过孔时牢记以下准则:

通过引入更多的平行过孔来降低寄生电容

必须将专用过孔连接到组件的每个引脚或焊盘。

尽可能使用地平面缝合。这为电流创建了更短的接地回路。

通孔减少了射频走线从一层到下一层的布线。

该设计允许您在内层和顶层接地层之间使用尽可能多的过孔。 这些过孔必须至少是信号波长的 1/20。

电源去耦

射频板需要降噪才能有效。这些电路板容易受到高频噪声的影响。因此,去除噪声是一项复杂的任务。其中一种方法是电源去耦。

选择去耦电容

该滤波器可消除电源引入电路的任何噪声。这些电容器称为去耦电容器。这些电容器连接到电源。

阻抗匹配应该是每个射频电路板不可或缺的一部分。连接去耦电容后,电路的阻抗应保持恒定。为避免阻抗变化,请遵循以下设计注意事项:

对于去耦,始终连接具有最小阻抗的电容器

要获得最小阻抗,请在自谐振频率(SRF)下运行电容器。电容器的SRF值将与其电容成反比。

寻找SRF接近噪声频率的电容器。

放置去耦电容

正确放置去耦电容至关重要。下面的电路显示了与IC并联放置的两个去耦电容器。

较高的电容器用于过滤低频噪声和存储能量。较低的电容器滤除高频噪声。这些是其他放置指南:

元件和去耦电容应放置在同一表面上。

将电容器与信号流路径平行放置。

每个电容器都应该有自己的接地通孔。

根据电容升序排列电容器。电容最小的电容离电源最近。

制造商和设计人员都需要更加关注射频板的设计和制造过程。DFM团队应遵循设计清单。这些板容易受到干扰和高频噪声的影响,因此即使是最轻微的错误也会对操作产生重大影响。这些方面和其他方法将帮助我们改进我们的设计。

丰乐壹博专业PCB设计、PCB Layout、PCBA一站式生产.

上一新闻:PCB设计的基本最佳规则

下一新闻:浅谈pcb设计规范